Ontwikkeling: 1989–2000

In 1989 dacht HP dat Reduced InstructionSet Computing (RISC)-architecturen vastzaten aan één instructie per cyclus. HP onderzoekers probeerden een nieuw type processorarchitectuur te creëren, later Explicly Parallel Instruction Computing (EPIC) genoemd, dat de processor in staat stelt om veel instructies in elke klokcyclus te gebruiken. EPIC gebruikt een vorm van zeer lange instructiewoord (VLIW) architectuur, waarbij 1 instructiewoord veel instructies had. Met EPIC controleert de compiler welke instructies tegelijkertijd gebruikt kunnen worden, zodat de processor de instructies kan uitvoeren zonder dat er ingewikkelde methodes nodig zijn om te zien welke instructies tegelijkertijd gebruikt moeten worden. Het doel van dit idee is om een betere inspectie van de code op het moment van compileren mogelijk te maken om te controleren of er extra mogelijkheden zijn voor meerdere uitvoeringen tegelijk, en om het ontwerp van de processor te vereenvoudigen en elektriciteit te besparen door de noodzaak van runtime planningsinstructies te elimineren.

HP dacht dat het niet goed was voor individuele bedrijfssysteembedrijven zoals HP om eigen processoren te maken, dus werkte HP in 1994 samen met Intel om de IA-64-architectuur te maken, gemaakt met de ideeën van EPIC. Intel wilde een grote inspanning leveren om de IA-64 te maken in de verwachting dat de resulterende processor door de meeste bedrijfssystemen zou worden gebruikt. HP en Intel hadden een grote ontwerpinspanning om het eerste Itaniumproduct, Merced, te maken in 1998.

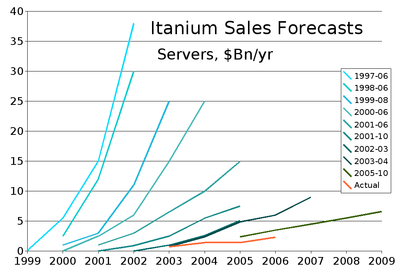

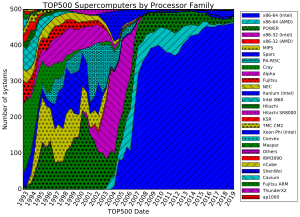

Tijdens de creatie dachten Intel, HP en andere industrie-analisten dat IA-64 zeer populair zou zijn in servers, werkstations en desktops, en op een dag RISC en Complex Instruction Set Computing (CISC) architecturen voor multi-purpose toepassingen zou vervangen. Compaq en Silicon Graphics stopten met het werken aan hun Alpha- en MIPS-architecturen om over te stappen op de Itanium-architectuur.

Veel groepen creëerden besturingssystemen voor Itanium, waaronder Microsoft Windows, OpenVMS, Linux en UNIX types zoals HP-UX, Solaris, Tru64 UNIX en Monterey/64 (de laatste drie waren nooit klaar met draaien op Itanium). In 1997 vonden velen dat de Itanium architectuur en de compiler moeilijker te gebruiken waren dan ze dachten. Technologische kwesties zoals de zeer hoge transistortellingen die nodig zijn voor de grote instructiewoorden en de grote caches. Er waren ook problemen met het project, omdat de twee delen van het team verschillende methoden gebruikten en iets andere prioriteiten hadden. Omdat Merced de eerste EPIC-processor was, had de oprichting ervan meer problemen dan het team had gedacht. Bovendien vereist het EPIC-concept verschillende compilercapaciteiten die nog nooit eerder waren gecreëerd, dus was er meer onderzoek nodig. []

Intel kondigde de naam van de processor, Itanium, aan op 4 oktober 1999. In slechts enkele uren tijd werd de naam Itanic als grapje gebruikt (een verwijzing naar de Titanic, het "onzinkbare" schip dat in 1912 zonk ("Itanium + Titanic = Itanic")). "Itanic" is ook gebruikt door The Register, en anderen, om te zeggen dat de multi-miljard-dollar investering in Itanium, en de vroege vraag daarmee, niets zou betekenen omdat ze dachten dat Itanium zou gaan falen.

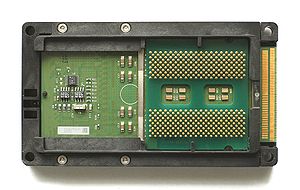

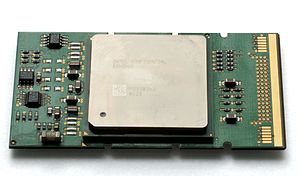

Itanium (Merced): 2001

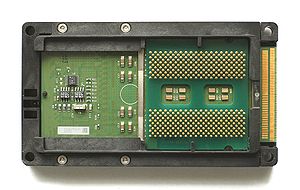

| Itanium (Merced) |

|

|

| Geproduceerd | Van juni 2001 tot juni 2002 |

| Gemeenschappelijke fabrikant(en) | |

| Max. CPU-kloksnelheid | 733 MHz tot 800 MHz |

| FSB-snelheden | 266 MT/s |

| Instructieset | Itanium |

| Aantal kernen | 1 |

| L2-cache | 96 KB |

| L3-cache | 2 of 4 MB |

| Contactdoos(sen) | |

| Kernnaam (-namen) | |

Tegen de tijd dat Itanium in juni 2001 op de markt kwam, waren de prestaties niet beter dan die van concurrerende RISC- en CISC-processoren. Itanium concurreerde met laagvermogensystemen (voornamelijk 4-CPU en kleine systemen) met servers op basis van x86-processoren, en met hoogvermogen zoals de POWER-architectuur van IBM en de SPARC-architectuur van Sun Microsystems. Intel verschoof Itanium naar het werken met de high-power business en HPC computing, en probeerde de succesvolle markt van x86 te kopiëren (d.w.z. 1 architectuur, veel systeemleveranciers). Het succes van de 1e processor versie was alleen met het vervangen van PA-RISC in HP systemen, Alpha in Compaq systemen en MIPS in SGI systemen, maar IBM maakte ook een supercomputer op basis van deze architectuur. POWER en SPARC waren sterk, en de x86-architectuur groeide meer in de bedrijfsruimte, vanwege de eenvoudigere schaalbaarheid en de zeer grote installatiebasis.

Slechts een paar duizend systemen met de 1e Itanium processor, Merced, werden verkocht, vanwege slechtere prestaties, hoge kosten en minder Itanium-gemaakte software. Intel zag dat Itanium meer native software nodig had om goed te kunnen werken, dus maakte Intel duizenden systemen voor onafhankelijke softwareleveranciers om hen te helpen met het maken van Itanium software. HP en Intel brachten de 2e Itanium processor, Itanium 2, een jaar later op de markt.

Itanium 2: 2002-2010

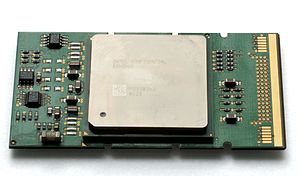

| Itanium 2 (McKinley) |

|

|

| Geproduceerd | Van 2002 tot 2010 |

| Ontworpen door | Intel |

| Gemeenschappelijke fabrikant(en) | |

| Max. CPU-kloksnelheid | 900 MHz tot 2,53 GHz |

| Instructieset | Itanium |

| Aantal kernen | 1, 2, 4 of 8 |

| L2-cache | 256 KB op Itanium2

256 KB (D) + 1 MB (I) of 512 KB (I) op (Itanium2 9x00-serie) |

| L3-cache | 1,5-32 MB |

| Contactdoos(sen) | - PAC611

- FC-LGA6 (LGA1248) (Itanium 9300-serie)

|

| Kernnaam (-namen) | - McKinley

- Madison

- Hondo

- Deerfield

- Montecito

- Montvale

- Tukwila

- Poulson

|

De Itanium 2-processor werd in 2002 uitgebracht, voor bedrijfsservers en niet alle high-power computing. De 1e versie van Itanium 2, codenaam McKinley, is gemaakt door HP en Intel. Het loste veel van de problemen van de 1e Itanium-processor op, die meestal werden veroorzaakt door een slecht geheugensubsysteem. McKinley had 221 miljoen transistors (waarvan 25 miljoen voor de logica), en was 19,5 mm bij 21,6 mm (421 mm2) en werd gemaakt met een 180 nm ontwerpproces, en een CMOS-proces met 6 lagen aluminium.

In 2003 bracht AMD de Opteron uit, die de eerste x86-64-architectuur (destijds AMD64 genoemd) implementeerde. Opteron was veel succesvoller omdat het een eenvoudige upgrade was van x86. Intel implementeerde x86-64 in 2004 in haar Xeon-processoren.

Intel heeft in 2003 een nieuwe Itanium 2-processor uitgebracht met de codenaam Madison. Madison gebruikte een 130 nm-proces en was tot juni 2006 de basis van alle nieuwe Itanium-processoren.

In maart 2005 kondigde Intel aan dat het werkte aan een nieuwe Itanium processor, codenaam Tukwila, die in 2007 zou worden uitgebracht. Tukwila zou 4 processorkernen hebben en zou de Itaniumbus vervangen door een nieuwe Common System Interface, die ook gebruikt zou worden door een nieuwe Xeon-processor. Later in dat jaar veranderde Intel de releasedatum van Tukwila naar eind 2008.

In november 2005 werkten de grootste Itanium-serverfabrikanten samen met Intel en vele softwareleveranciers om de Itanium Solutions-alliantie te creëren, om de architectuur te bevorderen en de softwareoverdracht te versnellen. De Alliance zegt dat haar leden tegen het einde van het decennium 10 miljard dollar zouden investeren in Itanium-oplossingen.

In 2006 leverde Intel Montecito (op de markt gebracht als de Itanium 2 9000-serie), een 2-core processor die ongeveer 2x zo goed presteert en 20% minder energie verbruikt.

Intel heeft de Itanium 2 9100-serie, codenaam Montvale, in november 2007 vrijgegeven. In mei 2009 werd de release voor Tukwila, de opvolger van Montvale, opnieuw gewijzigd, met een release voor OEM's gepland voor het eerste kwartaal van 2010.

Itanium 9300 (Tukwila): 2010

De Itanium 9300-serie processor, codenaam Tukwila, werd op 8 februari 2010 uitgebracht, met grotere prestaties en meer geheugen.

Tukwila maakt gebruik van een 65 nm proces, heeft tussen twee en vier kernen, tot 24 MB CPU cache, Hyper-Threading technologie en nieuwe geheugencontrollers. Het heeft ook double-device data correctie, wat helpt om geheugenproblemen op te lossen. Tukwila heeft ook Intel QuickPath Interconnect (QPI) ter vervanging van de Itanium bus architectuur. Het heeft een maximale binnen-processor bandbreedte van 96 GB/s en een maximale geheugenbandbreedte van 34 GB/s. Bij QuickPath heeft de processor ingebouwde geheugencontrollers, die het geheugen met behulp van QPI-interfaces besturen om te communiceren met andere processoren en I/O-hubs. QuickPath wordt ook gebruikt met Intel-processoren die de Nehalem-architectuur gebruiken, zodat Tukwila en Nehalem wellicht dezelfde chipsets kunnen gebruiken. Tukwila heeft vier geheugencontrollers, die elk meerdere DDR3 DIMM's ondersteunen via een aparte geheugencontroller, vergelijkbaar met de Nehalem Xeon-processor met de codenaam Beckton.

Itanium 9500 (Poulson): 2012

| | Dit artikel moet worden bijgewerkt. U kunt Wikipedia helpen door het te updaten. (Maart 2014) |

De Itanium 9500-serie processor, codenaam Poulson, is de opvolger van Tukwila en werd op 8 november 2012 uitgebracht. Intel zegt dat het de 45 nm procestechnologie overslaat en in plaats daarvan gebruik maakt van de 32 nm procestechnologie; het beschikt over 8 kernen, heeft een 12-brede issue-architectuur, multi-threading toevoegingen, en nieuwe instructies voor parallellisme, met inbegrip van virtualisatie. De Poulson L3 cachegrootte is 32 MB. De L2-cachegrootte is 6 MB, 512 I KB, 256 D KB per kern. De grootte van Poulson is 544 mm², minder dan de grootte van Tukwila (698,75 mm²).

Op ISSCC 2011 presenteerde Intel een document met de titel "A 32nm 3.1 Billion Transistor 12-Wide-Issue Itanium Processor for Mission Critical Servers". Gezien Intel's geschiedenis van het delen van details over Itanium microprocessoren bij ISSCC, verwijst dit document waarschijnlijk naar Poulson. Analist David Kanter speculeert dat Poulson een nieuwe architectuur zal gebruiken, met een meer geavanceerde vorm van multi-threading die maar liefst twee threads gebruikt, om de prestaties te verbeteren voor single threaded en multi-threaded werk. Nieuwe informatie werd vrijgegeven op de Hot Chips conferentie.

De nieuwe informatie claimt verbeteringen in multithreading, betrouwbaarheidsverbeteringen (Instruction Replay RAS) en enkele nieuwe instructies (thread prioriteit, integer instructie, cache pre-fetching, data access hints).

In Intel's Product Change Notification (PCN) 111456-01 werden 4 modellen van de Itanium 9500-serie CPU vermeld, die in een herziene versie van het document werden verwijderd. De onderdelen werden later opgenomen in Intel's Material Declaration Data Sheets (MDDS) database. Intel heeft later de referentiehandleiding voor Itanium 9500 gepost.

De modellen zijn:

| Bewerkersnummer | Frequentie |

| 9520 | 1,73 GHz |

| 9540 | 2.13 GHz |

| 9550 | 2.4 GHz |

| 9560 | 2,53 GHz |